# Validation of Translation to Optimized Machine Code

Thesis for the degree of Ph.D.

by

Raya Leviathan

Under the Supervision of Prof. Amir Pnueli

Presented to the Scientific Council of the Weizmann Institute of Science

August 25, 2004

## Acknowledgment

I would like to express my deep gratitude to my advisor, Prof. Amir Pnueli, for sharing with me his wisdom, knowledge, experience and confidence. His commendable insights and invaluable guidance inspired me all along my work.

Many thanks to Henny Sipma for her assistance in using the STeP tool, for providing me with relevant material and, for willingly adding features to suit my needs.

Special thanks to Orna Lichtenstein, for taking the time and effort to carefully read this thesis and related work. Her advised comments assisted me to improve my work.

Also, I would like to thank all the members of our formal verification group at the Weizmann Institute, for both the scientific atmosphere and the pleasant environment they have created.

Special thanks are relayed to my parents, Ester and Pinchas, who showed me the beauty of learning. My thanks are also conveyed to my children Yaniv, Thalma, Yarden and Roni for walking silently around the house, so as not to disturb me working. Their understanding and approval of the scarce quality time I could spend with them during my work, considerably contributed to the peace of mind I needed. In particular, I would like to thank Yaniv for his knowledgeable advice and help with regard to software issues, as well as for his enlightening comments to my work.

Finally, I would like to thank my husband, Nissan, for helping me at home with the kids and the dishes, for his encouragement during difficult times, as well as for his innumerable comments on my thesis.

# Contents

| 1        | Introduction                             | 1         |

|----------|------------------------------------------|-----------|

|          | 1.1 Background                           | <br>1     |

|          | 1.2 Related Work                         |           |

|          | 1.3 Contribution                         |           |

|          | 1.4 Overview                             |           |

| Ι        | Theoretical Framework                    | 11        |

| <b>2</b> | Transition Systems                       | 13        |

|          | 2.1 Programs and Translations            | <br>15    |

|          | 2.2 Correctness of Translations          |           |

| II       | Validating an EPIC Code Generator        | 19        |

| 3        | A Compiler Structure                     | 21        |

|          | 3.1 Validating Each Pass Separately      | <br>23    |

| 4        | EPIC Architectures                       | <b>25</b> |

| 5        | Validating the Translation               | 27        |

|          | 5.1 Block Programs                       | <br>27    |

|          | 5.2 The AVALIDATE Procedure              | <br>30    |

|          | 5.3 Soundness of the AVALIDATE Procedure | <br>33    |

| 6        | Loop Unrolling                           | 37        |

|          | 6.1 Description of the Optimization      | <br>37    |

|          | 6.2 Validating Loop Unrolling            |           |

ii CONTENTS

| 7  | Soft | tware Pipelining                                   | 43 |

|----|------|----------------------------------------------------|----|

|    | 7.1  | Architecture Definition                            | 43 |

|    |      | 7.1.1 Machine Registers                            | 43 |

|    |      | 7.1.2 Machine Instructions                         |    |

|    |      | 7.1.3 Architecture Support for Software Pipelining | 44 |

|    | 7.2  | Validation of the Optimization                     |    |

|    |      | 7.2.1 A General Software Pipelining Representation | 47 |

|    |      | 7.2.2 The General Idea                             |    |

|    |      | 7.2.3 Computing $\varphi$                          | 51 |

|    | 7.3  | An Example                                         | 55 |

|    | 7.4  | SPV: Software Pipelining Validator                 |    |

|    | 7.5  | Conclusions                                        |    |

| II | ı ·  | Validating an Industrial Compiler                  | 59 |

|    |      | <u>-</u>                                           |    |

| 8  | The  | e Programs and the Compiler                        | 61 |

| 9  | Sing | gleton Transition Systems                          | 63 |

|    | 9.1  | Correctness of Translations                        | 64 |

| 10 | Syn  | chronous Programs                                  | 67 |

|    | 10.1 | Synchronous Machine Code Programs                  | 68 |

|    |      | 10.1.1 Special Machine Instructions                | 70 |

|    | 10.2 | Synchronous C Programs                             |    |

| 11 |      | npressing a TS into a Singleton TS                 | 75 |

|    | 11.1 | Root Substitution                                  | 75 |

|    |      | The Annotation Algorithm                           |    |

|    | 11.3 | Soundness of Annotation                            | 77 |

|    | 11.4 | Producing a Compressed TS for C                    | 81 |

| 12 | The  | e MCVT Tool                                        | 83 |

|    | 12.1 | General Architecture of the Tool                   | 83 |

|    | 12.2 | Compact Expression Representation                  | 85 |

|    | 12.3 | The Formulas' Simplifier                           | 85 |

|    | 12.4 | The Code Pattern Recognizer                        | 87 |

|    |      | The Data Abstraction                               |    |

|    | 12.6 | Decomposing the Verification Conditions            | 88 |

| CC           | NTENTS                                                                                                                                                                                                                                                                                                                                                                                               | iii                                           |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|              | 12.7 Adaptation to CVC                                                                                                                                                                                                                                                                                                                                                                               | 88<br>89<br>90<br>90                          |

| 13           | Publications                                                                                                                                                                                                                                                                                                                                                                                         | 93                                            |

| A            | Loop Unrolling Validation- An Example  A.1 Assembly Code Semantics A.2 The Source and Target Programs A.3 Optimization Methods Applied in the Example A.4 Verification Process A.4.1 Source Transition System A.4.2 Target Transition System A.4.3 Adding an Auxiliary Variable to the Target System A.4.4 Control Abstraction A.4.5 Data Abstraction A.4.6 Invariants A.4.7 Verification Conditions | 102<br>105<br>105<br>106<br>110<br>110<br>111 |

| В            | IA64 Pipelined Loop                                                                                                                                                                                                                                                                                                                                                                                  | 15                                            |

| $\mathbf{C}$ | Translation Validation of a C Program                                                                                                                                                                                                                                                                                                                                                                | 17                                            |

| $\mathbf{D}$ | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                 | 21                                            |

iv CONTENTS

# List of Figures

| 3.1        | Compiler structure                                        | 22  |

|------------|-----------------------------------------------------------|-----|

| 5.1        | A block program and its transition system                 | 31  |

| 6.1        | General form of loop unrolling                            | 38  |

| 6.2        | Adding an auxiliary variable                              | 39  |

| 6.3        | Verification condition for the first copy                 | 40  |

| 6.4        | Verification condition for copy Number C                  | 40  |

| 7.1        | C source program                                          | 45  |

| 7.2        | Unoptimized target code                                   | 46  |

| 7.3        | Loop pipeline schedule                                    | 47  |

| 7.4        | Target pipelined loop                                     | 48  |

| 7.5        | General form of a pipelined loop                          | 49  |

| 7.6        | Using invariants to validate the translation - an example | 50  |

| 7.7        | The States at the end of target prologue iterations       | 50  |

| 7.8        | Algorithm for computing $\varphi$                         | 52  |

| 7.9        | Verification conditions for a pipelined loop              | 53  |

| 7.10       | Symbolic evaluation of $\varphi$ - an example             | 54  |

| 10.1       | Machine code example - 1                                  | 72  |

|            | Machine code example - 2                                  | 72  |

| 10.2       |                                                           |     |

| 11.1       | Root substitution applied to program P                    | 76  |

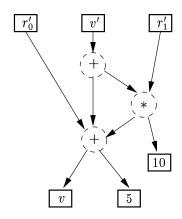

| 12.1       | Compact expressions tree                                  | 85  |

| A.1<br>A.2 | The C program and its corresponding block program         |     |

| B.1        | IA64 assembly code                                        | 115 |

| 118          |

|--------------|

| variable 119 |

|              |

| ontinued in  |

| 122          |

| ontinued 123 |

| ,            |

# Chapter 1

### Introduction

### 1.1 Background

There is a growing awareness of the importance of formally proving the correctness of safety critical portions of software systems. However, proving the correctness of the implementation, written in a high level language, is not sufficient. It should also be verified that whatever correctness has been achieved on the higher level, is not impaired in the translation done by the compiler. This is the reason that standards and regulations require to qualify a compiler, to be used in a safety critical system.

To ensure mathematical correctness of a compiled code, several methods are possible:

- Verifying the compiler program, using the formal semantics of the source program and the target processor machine code, as well as the knowledge about the compiler internal structure and algorithms.

- Enhancing the compiler to produce assertions, whose validity is an evidence to the correctness of the compiler, or of a specific translation.

- Validating each translation as it is generated, by comparing the source program to its translated version and, formally verifying their equivalence.

Formally verifying a full-fledged compiler is a huge engineering effort due to its size, evolution over time and possibly, proprietary considerations. It also requires a freeze of the compiler development process. In many cases, the qualified compiler is inferior to its unqualified updated version, with regard to the performance of the translation, as well as to the number of errors, since qualification does not guarantee the mathematical correctness of the tool. As far as modifications to the compiler are concerned, they may be implemented on an open source compiler. However, should the compiler be a commercial one, such modifications are rendered impossible.

In view of the above considerations we choose the **translation validation** [PSS98c] approach, which allows an alternative to the verification of translators in general and, of compilers in particular. It offers the validation of each specific translation, whenever the compiler is invoked. Another advantage of this approach is derived from the fact that most industrial compilers have known bugs, yet it is rather difficult to identify the code in the application source program, that exposes such a bug. The translation validation approach allows the use of such a compiler in the development of a safety critical system, by ensuring that any translation error is discovered.

Translation validation should handle four kinds of differences between the source program and its translation:

- Syntactic differences.

- Semantic differences (e.g. synchronous languages versus sequential languages).

- Program transformations (code optimizations).

- Variables names and representation differences.

When a straightforward translation is involved, without optimizations, the validation of the translation is basically a syntactic issue. This task becomes much more difficult when transformations are applied and, change the source program flow of control, as well as the source language data-structures and their semantics. This is the case of **optimizing compilers**.

The importance of compiler optimizations is increasing, together with the development of modern CPU architectures, such as RISC (Reduced Instruction Set Computer), ILP (Instruction Level Parallelism) or EPIC (Explicitly Parallel Instruction Computing). It is the task of optimizing compilers to ensure correct and efficient use of the CPU. Without optimizations, only a small fraction of the computing power of these CPUs can be exploited. For

these architectures, as opposed to previous generations of architectures, a significant part of the optimizations is done at the code generation stage of the compiler. It is the aim of this research, among other things, to handle the validation of this kind of program transformations.

Another challenge of this research is to handle an **industrial environment**, where the source language, the processor, the compiler as well as the applications, are all industrial software. However, in order to be useful to the industrial sector, a **fully automatic process** is obligatory.

Our main goal is to develop a method, which can validate the machine dependent stage of an optimizing compiler, with a focus on advanced CPU architectures. Since we believe that automation is a key feature of such a method, we also want to check and demonstrate the feasibility of a fully automatic process. Another issue we want to investigate is the kind of assistance needed from the compiler in order to achieve this goal. To complete the validation process, we should provide the needed decision procedures, by developing our own algorithms and using existing tools.

We chose two extreme cases of the problem:

- Case 1: Verifying the optimized translation of programs, written in a general imperative language (C subset) for an EPIC type CPU. This problem is characterized by aggressive loop optimizations in the code generation stage of the compiler, in particular, loop unrolling and software pipelining. The compiler under research is an open source compiler and provides internal information upon request.

- Case 2: Verifying a translation from *synchronous* C programs, compiled with a commercial compiler, into an optimized code for the PowerPC family of architectures. Here, the only available information is the binary output of the compiler. The lack of assistance from the compiler, imposes limitations on the language of the source programs we handle. Synchronous programs are used very often to design safety-critical systems. These programs, by definition, have no loops, except for one implicit external loop in their main function. This fact helps us to overcome the difficulties raised by the industrial compiler. Thus another characterizing description for synchronous C programs is "loop-free programs".

Along with developing a theoretical basis and methods, which can handle these two problems, it was required to develop tools, capable of producing a common semantics for different languages (C language as well as IA64 and, PowerPC assembly languages). These tools should automatically produce proof obligations, in order to establish the correctness of the translation. Algorithmic simplification is needed as well, to make the proof obligations provable by external validity checkers, to which our tools should interface.

### 1.2 Related Work

Several methods are used in order to mechanically solve the translation validation problem. Most methods start by constructing a data abstraction mapping. Then, either proof obligations or checkers, are produced. The proof obligations can be validated by an "off the shelf" validity checker, or by a theorem prover [ZG97, GZ99, GZG00, GZ00]. In other cases, the validation process is based on heuristics and, interaction between the heuristic part and the decision procedures, or the formulas' simplifier [Nec00, RM00]. Yet another approach, lets the compiler produce the proofs that are needed to establish its correctness [RM00, GZ00].

The CVT tool [PSS98a, PSS99] is an example of an industrial quality translation validation tool. It demonstrates an automatic procedure for validating the translation from the synchronous language SCADE to a sequential C program. Its main problems are the semantic difference between a synchronous language and a sequential C code, as well as the data abstraction mapping. The proof obligations that are produced, include equalities and uninterpreted functions, relying on the fact that the compiler does not change the way arithmetic functions are applied. The final validation is done by general decision procedures. Part of our thesis is to further validate the translation of the C programs, that are produced from SCADE source, to optimized machine code.

The VOC project [ZPFG02] concentrates on the translation of C programs by an optimizing compiler, where the investigated optimizations are machine independent. The language of both source and target systems is the intermediate representation of the compiler. Two different proof rules are presented: one which handles loop transformations and, another for "structure preserving" transformations. The first proof rule ensures the correctness of non "structure preserving" transformations, which are permutations on the loop iterations' order. The other proof rule is based on Floyd's inductive-assertion method [Flo67] and, proves the correctness of other machine independent

transformations. The methodology we are using in part II of our work is the same as the one used in VOC. However, applying it to EPIC code generator introduces new problems. For example, the EPIC-specific transformations of software pipelining and loop unrolling which occupy a major part of the thesis are not covered by the VOC project.

Other works are done as part of the Verifix project [GZ99, GZG00]. These rely on the PVS theorem prover [COR<sup>+</sup>95], in order to mechanize the verification, but full automation is not supported. One part of the Verifix project concentrates on compiler back-ends. It formalizes the semantics of the assembly code, as well as of an intermediate representation, using higher-order logic which are supported by PVS, whereas our goal is to use formulas whose validity is decidable. Another aspect of the Verifix project, which relates to our work, is the program checker approach. This approach, when applied to compiler verification, is the same as translation validation, since a validation checker is produced for each translation. However, contrary to our work, the checker is produced by the compiler. In the work described in [RM00], it is the compiler that produces the proofs, but the validity of the proof is established by the tool itself. The correctness proof consists of two sub-proofs: a sub-proof which shows that the analysis of the input program produces a correct result and, a sub-proof that establishes an equivalence between the original and the transformed programs.

Another method is described in [Nec00]. It is based on heuristics and a special purpose simplifier. The latter is composed of inference rules and is built in a tool. The tool is able to validate translations automatically. It can handle a wide range of optimizations, but as reported, may fail for loop unrolling and does not handle software pipelining. This work also uses the intermediate representation and, validates each optimization pass separately.

All the above mentioned works use compiler assistance, to some degree. It is a major challenge in translation validation research to minimize this dependence.

### 1.3 Contribution

#### **Theoretical Framework**

The theoretical framework, is based on [MP95], [ZPG00], [ZPL01] and [ZPFG02]. In this thesis, we define block programs syntax and semantics, which we use to formulate the problem. Based on this formulation we describe a criterion for the validation of a translation. This criterion also holds for infinite computation (as usually the case for reactive systems). We prefer to use basic blocks rather than basic paths, because we handle assembly language programs. We restrict the validation procedure in order to ensure that the validity of the verification conditions can be decided algorithmically. The framework includes the following items:

- A general syntax and formal semantics of *block programs*, for machine code programs. As semantics we use transition systems [MP95].

- A definition of correct translation for terminating and non-terminating programs.

- The AVALIDATE (Assembly Validate) procedure, which is an adaptation and extension of the Validate procedure of [ZPG00], [ZPL01] and [ZPFG02], was developed to support *block programs* and advanced machine specific loop optimizations. We prove the soundness of the procedure, for both terminating and non-terminating (though "correct") programs. We formulate the procedure to produce only formulas of decidable logics.

- In order to validate the translation of synchronous programs we define compressed transition system and a simplified procedure that ensure the correctness of the translation.

In this work we choose to handle two cases of the problem, as described hereby.

# Case 1: Validating the Code Generator Optimizations of an EPIC type CPU

We developed algorithmic methods that cooperate with the AVALIDATE procedure, based on internal information from the compiler, to prove the validity of machine specific loop optimizations - loop unrolling and software pipelining. It should be emphasized that although information from the compiler is used, the soundness of the method does not depend on the correctness of this information. An algorithm to produce program invariants, which is based on symbolic evaluation was developed and enables the validation of software pipelining optimizations. The SPV (Software Pipelining Validator) tool that we developed, demonstrates the automatic validation of software pipelining optimizations, which are performed by the SGI-PRO64 [GADT00] compiler for Intel's IA64 processors family [Int]. SPV uses the intermediate representation of the code generator, that is obtained from the compiler. It produces verification conditions, that are validated by the CVC [SBD02] validity checker. At the early stages of the project, we used STep[BBC<sup>+</sup>95], to check the basic concepts, and verify manually produced verification conditions. Our method is based on dividing the program into blocks, which are usually small. Therefore, the verification conditions are small as well. The implementation supports a subset of the IA64 architecture and, handles small programs. No performance problems were identified in the application of the tool.

### Case 2: Validating the Translation from Synchronous C Programs to PowerPC Binary Code, by a Commercial Compiler

As opposed to case 1 above, here we could not apply the AVALIDATE procedure. The reason is that the basic building blocks of the validation methodology that underlies AVALIDATE, are the control and data abstraction mapping, between the source and the target (translated) systems. In case 1 above, we use the compiler internal information that can be obtained upon request, which assists us to construct these abstractions, whereas in the present case, there is no access to internal information of the commercial compiler. Therefore, we had to develop a different approach.

Hence, we developed the Annotation algorithm. This algorithm produces a compressed form of a block program without loops and thus, the need to map the control and local variables is eliminated. The algorithm performs forward analysis of the assembly code, while annotating the machine instructions with the conditions on the input variables values, under which they are executed in a specific computation. The soundness of the algorithm is proved.

However, constructing the abstraction mapping between the observable variables of the source and the target systems, is still required. This is achieved by using standard debug symbolic information. Due to the presentation of both source and target systems in a compressed form, it is easy to break up the verification conditions, in order to handle each observable variable by a different verification condition.

Another problem we had to overcome, is the fact that the compiler uses special machine code sequences, which contains bit manipulation machine-instructions, to optimize some C language integer operations in the source program. In order to solve this problem, we developed a mechanism that interprets these sequences correctly, yet in a simplified way, so as to shorten the run time of the validity checker.

The tool we developed - MCVT (Machine Code Validation Tool) - validates the translation done by the DiabData C compiler of WindRiver [Dia], for the PowerPC CPU. It produces verification conditions and then invokes CVC to prove their validity. The MCVT tool is capable of proving the validity of the translation, of non-trivial programs, as is shown in the SafeAir case study, which is a simple communication controller program. In some cases, we expect the MCVT tool to fail in validating a correct translation within reasonable time limits. We believe that these cases can be solved, by further applying simplification methods to the verification conditions, produced by MCVT.

### 1.4 Overview

The methods we developed handle a variety of processor architectures. The tools we developed are retargetable to different processors and support already a couple of machine codes (IA64 and PowerPC). The proof obligations that are produced are formulas, whose validity is decidable. The tools are re-configurable to use different validators.

1.4. OVERVIEW 9

This thesis is organized in three parts, where the common theoretical framework is described in Part I, validating the code generator optimizations of an EPIC type CPU is detailed in Part II and, validating the translation from synchronous C programs by a commercial compiler is presented in Part III.

# Part I Theoretical Framework

# Chapter 2

### **Transition Systems**

This chapter describes the common framework of the two cases we handle in this thesis. In the following chapters we extend the relevant theory, separately for each case.

In order to be able to check that the "meanings" of two programs are equivalent, the semantics of both programs should be formalized by common means. Transition Systems, as introduced in [MP95] turned out to be a convenient common semantics. In this chapter we describe transition systems. In later chapters of this work we describe the syntax of different programming languages and their corresponding transition systems.

We assume that all variables that describe states of the program, or that appear in formulas specifying properties of programs, are taken from a universal set of variables  $\mathcal{V}$ , called the *vocabulary*. Variables in  $\mathcal{V}$  are typed, where the type of a variable such as *boolean* or *integer*, indicates the domain over which the variables range. In particular, we assume that, for each  $x \in \mathcal{V}$ , its *primed version* x' is also in  $\mathcal{V}$ . To define the syntax of transition systems, we use the language  $\mathcal{L}$ , which is the language of first-order logic without quantifiers over  $\mathcal{V}$ , with arithmetic functions, the *ite* (*if-then-else*) and *case* operators, the natural order of integers and booleans, uninterpreted functions, arrays and constants. For arrays, the operations with and [] are part of the language  $\mathcal{L}$ . Expressions in this language are constructed out of variables of  $\mathcal{V}$  and constants, to which functions and operations are applied. Expressions whose value is of integer type are *integer expressions* and, those whose value is boolean are *conditional expressions* (also called assertions). The array operation with is used to update an element of an array and []

is used to get a value of an array element. For example, for an array a of integers, the expression a with([2]:5)[2] has the integer value 5.

Let  $V \subseteq \mathcal{V}$  be a finite set of typed variables. We define a V-state s to be a type-consistent assignment of  $\mathcal{V}$ , assigning to each variable  $x \in V$  a value s[x] over its domain. We denote by  $\Sigma_V$  the set of all states of V. The value of an expression  $Exp(x_1,\ldots,x_n)$  in state s, where  $x_1,\ldots,x_n \in V$ , is denoted by s[Exp] and, is defined as  $Exp(s[x_1],\ldots,s[x_n])$ . For an assertion p over V we use the notation  $s \models p$  to denote that p holds in state s. We use the notion  $\langle s^1, s^2 \rangle \models R$  to denote that the pair of states  $\langle s^1, s^2 \rangle$ , where  $s^1 \in \Sigma^1, s^2 \in \Sigma^2$ , belongs to the binary relation  $R \subseteq \Sigma^1 \times \Sigma^2$ .

The system - A transition system (TS)  $S = \langle V, O, \beta, \Theta, \rho \rangle$  consists of the following components:

- $V \subseteq \mathcal{V}$  is a finite set of typed variables. One of the variables,  $\pi \in V$ , is the *control variable* which represents the location of the control of the program. 0 is the *entry location* value. *exit* is the *exit location* value.

- $O \subseteq V$  is the set of observable variables. The observable variables are the variables which are visible to the external world. An observation is a projection of a state  $s \in \Sigma_V$  on the observable variables. We denote by Obs the set of observations.

- $\beta$  an observability condition. An assertion characterizing the states which should be observed. It is required that  $\Theta$  implies  $\beta$ , i.e. all initial states are observable. A state satisfying  $\beta$  is called an observable state.

- $\bullet$   $\Theta$  is an assertion characterizing the initial states of the system.

- $\rho$  transition relation. This is an assertion  $\rho(V,V')$ , relating a state s to its successor s', by referring to both unprimed and primed versions of the state variables. The transition relation  $\rho(V,V')$  identifies state s' as a successor of state s if  $\langle s,s'\rangle \vDash \rho(V,V')$ , where  $\langle s,s'\rangle$  is the joint interpretation which interprets  $x\in V$  as s[x] and, x' as s'[x]. Thus, for example, the transition relation may include "y'=y+1" to denote that the value of the variable y in the successor state, is greater by 1 than its value in the previous state.

In writing a transition relation, we often use the notation Pres(U) for  $U \subseteq V$  which is an abbreviation for  $\bigwedge_{v \in U} (v' = v)$ , stating that all U variables are preserved.

Computations - A computation of a transition system  $S = \langle V, O, \beta, \Theta, \rho \rangle$  is a maximal-length finite or infinite sequence of states  $\sigma : s_0, s_1, \ldots$ , starting with an initial state  $s_0 \models \Theta$  and such that every two consecutive states are related by the transition relation, i.e.  $\langle s_i, s_{i+1} \rangle \models \rho$  for every  $i \ 0 \le i, i+1 < |\sigma|^1(|\sigma| \le \infty)$ . A finite computation is called terminating if its last state is observable.

**Observable behavior** - In order to formally define the external behavior of a transition system, we use *observation trajectory*, which defines **when** and **what** is externally observable during a computation. Given a computation  $\sigma: s_0, s_1, \ldots$ , the observation trajectory corresponding to  $\sigma$  is obtained by taking the subsequence of observable states and projecting each of them on the observable variables O.

### 2.1 Programs and Translations

In this work we handle a few types of programming languages, the translation of one into the other and, transformations of programs in the same programming language. Each program P has a **syntactic description** and, **formal semantics** which is expressed by a **transition system**. Let P be a program written in a programming language PL and let the transition system  $S^P$  express the semantics of program P. We say that  $S^P$  is the transition system of program P. A translation that is done by an optimizing compiler, includes transformations of a source program  $P^S$  into a target program  $P^T$ , in the same programming language, usually in order to decrease the run-time of the program (optimization transformation). It also includes transformations of a source program into a target program in a different, lower level programming language.

<sup>&</sup>lt;sup>1</sup>Let  $\sigma: s_0, \ldots, s_{k-1}$  be a finite sequence, then  $k = |\sigma|$  is the *length* of the sequence of states  $\sigma$ . When  $\sigma$  is infinite  $k = |\sigma| = \infty$ . In both cases an element of the sequence is  $s_i$ ; where  $0 \le i < |\sigma|$ .

To examine the correctness of a translation, we have to check the semantics of the source and target systems, and ensure the source semantics is preserved by the target. Thus, we consider the transition systems of the relevant source and target programs and require that certain relations hold between these systems. A similar approach can be found in other works on compiler verification, e.g. [PSS98c], [GZ00]. In the following subsection we define the correctness of a translation, based on the transition system semantics of the source and target programs, regardless of their programming languages. Later in this thesis, we describe syntax and transition system semantics of programs in specific programming languages and apply the notion of a correct translation.

### 2.2 Correctness of Translations

Informally, a correct translation needs only to ensure the preservation of the observable behavior [ZG97]. A target system is a correct translation of a source system, if every external behavior that exists in the target system, also exists in the source system. This characteristic is formalized by the notion of refinement [EdR<sup>+</sup>99].

Let  $S^S = \langle V^S, O^S, \beta^S, \Theta^S, \rho^S \rangle$  and  $S^T = \langle V^T, O^T, \beta^T, \Theta^T, \rho^T \rangle$  be two systems to which we refer as the *source* and *target* systems, respectively. Let  $\tau = \tau \langle O^S, O^T \rangle$  be an assertion to which we refer as the *translation mapping*. Usually, the translation mapping expresses values of source observables in terms of target observables.

A source observation  $o^S \in Obs^S$  and a target observation  $o^S \in Obs^S$  are said to be  $\tau$ -related if  $\langle o^S, o^T \rangle \vDash \tau$ .

We define system  $S^T$  to be a  $\tau$ -refinement of system  $S^S$  if, for every target observation trajectory  $\omega^T: o_0^T, o_1^T, \ldots$ , there exists a source observation trajectory  $\omega^S: o_0^S, o_1^S, \ldots$ , such that

- 1.  $|\omega^T| = |\omega^S|$ , i.e., they are both infinite or are both finite and of equal lengths,

- 2. For every  $i < |\omega^T|$ ,  $o_i^S$  and  $o_i^T$  are  $\tau$ -related.

Refinement means that for every computation of the target system, there exists a corresponding computation of the source system, in the sense that

both computations assume related values of the corresponding observable variables, at their observable states.

The definition of refinement, allows for finite and infinite computations in both the source and target systems. We include infinite computations, in order to support translations of reactive programs which run forever. For the same reason, we do not enforce determinism, i.e. for one initial state, we allow more than one computation to be possible. We say that a target program  $P^T$  is a correct translation of a source program  $P^S$ , if the transition system  $S^T$  of  $P^T$  refines the transition system  $S^S$  of  $P^S$ .

It should be emphasized, that since we choose the **translation** validation approach [PSS98c], rather than **translator** validation, we are not concerned with the compiler (translator) program validity. The **translation validation problem** is the problem of proving that a target transition system is a refinement of a source transition system. In this work we developed methods to establish refinement between source and target systems.

# Part II Validating an EPIC Code Generator

# Chapter 3

# A Compiler Structure

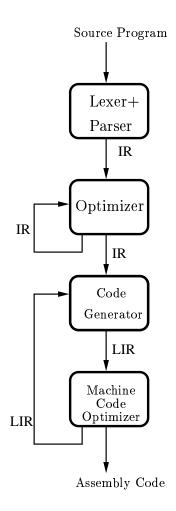

The translation validation method we describe in this part, relies significantly on our knowledge of compiler structure and on information that the compiler provides upon request. For this reason, we include a brief description of a compiler structure. This description is based on [ASU88] and [GADT00]. A typical structure of an EPIC compiler is shown in Fig. 3.1. Each block in the diagram represents a compiler phase. After syntax and semantics analysis, most compilers generate an *intermediate representation (IR)* as a program for an abstract machine.

A basic block is a sequence of consecutive statements, in which flow of control enters at the beginning and leaves at the end, without halt or a possibility of branching, except at the end. Basic blocks are the building blocks of the IR. Commonly used IR is a graph representation called a flow graph. Nodes of the flow graph are basic blocks, hence represent computations, and the edges represent the flow of control.

The optimizer phase attempts to improve the intermediate representation, resulting in a faster running machine code. A common practice in compilers' construction, is to perform each optimization in a different pass. Both the input and the output of an optimization pass are IRs. Some of the passes are executed more than once. The optimized IR is moved on to the code generator phase, which usually produces the final code. The machine code optimizer characterizes EPIC (Explicitly Parallel Instruction Computing) compilers. It applies optimizations that highly depend on the machine architecture and the exact code issued. These optimizations include register allocation, instruction scheduling, loop unrolling, predicating instructions,

Figure 3.1: Compiler structure

use of speculative load instructions and software pipelining. The machine code optimizer uses a *low level intermediate representation* (*LIR*), which is closer to the concrete architecture, and is used as the interface between its passes. The output of this compiler phase is the final assembly code.

### 3.1 Validating Each Pass Separately

As mentioned above, optimizers usually have many passes. The code generator of SGI-PRO64 compiler makes no exception. Based on this, we decide to validate each pass of the code generator separately, knowing that refinement is a transitive relation. I.e., let  $S^1$ ,  $S^2$ ,  $S^3$  be transition systems, then if  $S^2$  refines  $S^1$  and  $S^3$  refines  $S^2$ , then  $S^3$  also refines  $S^1$  [EdR<sup>+</sup>99]. The translation validation tool knows which optimization is applied on the target code in each pass and benefits from this knowledge. The LIR that the code generator produces in each pass is annotated with data. The validator tool uses this data to conclude which optimizations are applied, as well as their exact application details.

# Chapter 4

### **EPIC Architectures**

EPIC architecture is a way of achieving high instruction level parallelism, with reduced hardware complexity [KSR00]. The principal way of reducing the hardware complexity is by exposing the parallel micro-architecture to the compiler, using a processor model which provides an abstract description of the processor. Parallel execution, as well as latencies, are exposed to the compiler. The responsibility of achieving parallel execution is shifted from the hardware to the compiler. The cost of simplifying the hardware is complicating the compiler in general and the code generation stage, which is responsible for adjusting the code to the specific target, in particular.

We describe here some of the special features of EPIC architecture, in order to show the kind of problems that it raises for to the translation validator.

- Parallel execution A typical EPIC processor allows the parallel execution of some instructions. It is the compiler's responsibility to bundle instructions together, in order to be executed in parallel and, to ensure that access to registers is consistent and legal.

- Speculative execution In some cases the execution of an instruction may be discovered as erroneous and therefore, the effect of this execution should be canceled. This feature is called *speculative execution*. It is the compiler's responsibility to use this execution mode correctly.

- Register renaming Registers' names are changed (logically the register file is rotated), so that the very same instruction actually affects

different registers in two different executions.

- Software pipelining support (see section 7.1).

- Predicated instructions The execution of an instruction depends on a bit predicate. The compiler generates code that assigns values to this predicate.

We choose to concentrate on two main loop optimizations: loop unrolling and software pipelining, which use most of the advanced features in the list above. For loop unrolling we use the TRIMARAN compiler [TR0]. This compiler produces code for the research architecture PlayDoh [SRM<sup>+</sup>94]. To demonstrate validation of software pipelining we use the open source SGI-PRO64 [GADT00] compiler, which produces code for the industrial EPIC processor IA64 of Intel [Int].

# Chapter 5

# Validating the Translation

We first define a general syntax for machine code programs, as well as their semantics, using transition systems. These definitions do not include the details of a specific machine code, but rather serve as an abstract model which fits most of the processors we know. We describe a general procedure to validate optimizations of machine code programs, and prove the soundness of this procedure. The following chapters describe how loop unrolling and software pipelining optimizations are validated, using this procedure. Finally, we describe the tool SPV (Software Pipelining Validator), that automatically verifies loop pipelining optimization for the SGI-PRO64 compiler and the IA64 architecture.

#### 5.1 Block Programs

The machine code programs that we define here, are similar to flowchart programs [Flo67, Man72, LS84]. However, we prefer to use a syntax which is closer to the machine code.

An instruction Inst, is a legal machine instruction of the underlying physical processor. An instruction changes the state of the processor (the machine state), by assigning new values to the processor memory and registers. We divide the group of possible instructions to three subgroups, as follows:

1. Procedure instructions which are procedure calls. They have the following form:

• call crocedure-name>

An example of a procedure instruction is a call to print procedure which prints memory variables values.

- 2. branch instructions which have one of the two forms:

- branch < condition > < label > a conditional branch, where < label > is of type integer and, < condition > is a boolean expression.

- branch < label> an unconditional branch where < label> is of type integer.

The < label > is the branch instruction destination.

3. regular instructions of the form  $x:= \langle expression \rangle$  which are assignment instructions. (e.g. x:= a+1).

A block is a finite sequence of instructions  $B = Inst_1, \ldots, Inst_k$ . A block that contains a procedure instruction, may not contain any other instruction. Only the last instruction of a block may be a branch or a function instruction. The rest of the block's instructions are regular instructions. Also, only the first instruction of a block may be the destination of a branch instruction. A block program is a finite sequence of blocks  $P = B_0, \ldots, B_n$ , where the blocks are sequentially indexed. The index of a block is its label. The definition of a block conforms with the one of a basic block that is found in chapter 3.

In one block, at most one assignment is allowed for each variable. The meaning of a sequence of regular instructions in one block, is the simultaneous assignment of the expressions' values to the variables on the left side of the assignment. The framework built in Chapter 11 is the reasoning behind these restrictions.

Let  $P = B_0, \ldots, B_n$  be a block program, then  $B_0$ , the block whose index is 0, is the entry block. Sometimes we call this block  $B_{entry}$ . Each block  $B_i$ ,  $i = 0, \ldots, n$  of a program may have one or two successors, denoted by succ(B). If the last instruction of  $B_i$  is regular, then  $succ(B_i) = \{i+1\}$ . If the last instruction is an unconditional branch with destination j, then  $succ(B_i) = \{j\}$ . If the last instruction is a conditional branch with destination j, then  $succ(B_i) = \{j, i+1\}$ . The entry block is not a successor of any block of the program. We assume an additional implicit empty block  $B_{exit}$ , whose index is the exit location of the program. It is the exit block. A branch

29

instruction with destination i > n is equivalent to a branch instruction with destination exit. Let Proc(P) denote the indices of blocks which consist of procedure instructions.

Each block program P, corresponds to a transition system  $S^P = \langle V, O, \beta, \Theta, \rho \rangle$  where:

- V: {v<sub>1</sub>,..., v<sub>m</sub>} ∪ {pc} is a finite set of system variables. V includes all the program variables, where pc ∈ {0,..., n, exit} is the control variable. Its value denotes the index of the block in which control currently resides. pc stands for program counter. When the location of control equals a block's label, this block is about to be executed. Block label i and block name B<sub>i</sub>, are used interchangeably.

- O: The observable variables are memory variables.

- $\beta: pc \in \{0, exit\} \cup Proc(P)$ . This identifies the entry, exit and calllocations as locations at which we wish to observe the values of the observable variables. Since  $\beta$  depends only on pc, we will write  $\beta(i)$  or  $i \in \beta$  to denote that pc = i implies  $\beta$ .

- $\Theta$ : The initial condition assertion.  $\Theta \to pc = 0$ .

- $\rho$ : The transition relation.

Each block  $B_i = Inst_1, \ldots, Inst_k$  in the program is associated with a block transition relation:

$$\rho_i(V,V'): pc = i \wedge \bigwedge_{v \in V - \{pc\}} v' = Exp_v(V) \wedge pc' = comput\_pc(V),$$

where:

1. If there is a regular instruction in  $B_i$  such that  $\mathbf{v} := \mathbf{Exp}(\mathbf{V})$ , then  $Exp_v(V)$  is  $\mathbf{Exp}(\mathbf{V})$ , otherwise  $Exp_v(V)$  is  $\mathbf{v}$ . In case of data dependencies within a block, updated values replace the corresponding variables in  $Exp_v(V)$ . Recalling that there is at most one assignment for each variable, in a block,  $Exp_v(V)$  is well defined.

2.

$$compute\_pc(V) = \begin{cases} \textbf{ if } & \text{the block's last instruction is} \\ & \text{regular or a function} \\ \textbf{ then } & pc+1 \\ \textbf{ else if } & \text{the block's last instruction is} \\ & \text{`branch } < \text{label} > \text{`} \\ \textbf{ then } & label \\ \textbf{ else if } & \text{the block's last instruction is} \\ & \text{`branch } < \text{condition} > < \text{label} > \text{`} \\ \textbf{ then } & ite(condition, label, pc+1) \end{cases}$$

The program transition relation is  $\rho = \bigvee_{i=0}^{n} \rho_i(V, V')$ .

Two consecutive states in a computation of a block program, correspond to the machine states before and after the execution of one block. No transition relation is associated with the exit block.

Claim 1 Every computation  $\sigma: s_0, \ldots, s_i, \ldots$  of a block program, corresponds to a finite or infinite sequence of blocks' labels:  $B_0, \ldots, B_{j_i}, \ldots$ , where  $j_i = s_i[pc], B_{j_{i+1}} \in succ(B_{j_i})$  and  $\langle s_i, s_{i+1} \rangle \models \rho_{j_i}$ . If the sequence is finite, then its last block is  $B_{exit}$  (i.e. the exit block).

**Proof.** A direct consequence of the soundness proof of the inductive assertion method by Floyd [Man74] ■

Figure 5.1 shows a block program and its corresponding transition system.

#### 5.2 The AVALIDATE Procedure

Let  $P^S = B_0^S, \ldots, B_m^S$  and  $P^T = B_0^T, \ldots, B_n^T$ , be a source block program and a target block program respectively, with the corresponding transition systems  $\mathcal{S}^S = \langle V^S, O^S, \beta^S, \Theta^S, \rho^S \rangle$  and  $\mathcal{S}^T = \langle V^T, O^T, \beta^T, \Theta^T, \rho^T \rangle$ . As a convention, we use capital letters to indicate a source program variable (e.g. PC) and, small letters for a target variable (e.g. PC). We assume that there is a 1-1 correspondence between the source and the target observable variables and that the translation relation  $\tau$  is given by  $\tau: O = o$ . Based

| Block Program       | Transition System                                                   |

|---------------------|---------------------------------------------------------------------|

| L0: s := 0; i := 0; | $V = \{s, i, a, pc\}$                                               |

| L1: s := a[i]+s;    | $O = \{a, b\}, \beta : pc \in \{0, 2, exit\}$                       |

| i := i+1;           | $\Theta: pc = 0$                                                    |

| branch (i<100) L1   | $\rho: (pc = 0) \land (i' = 0) \land (s' = 0) \land (pc' = 1) \lor$ |

| L2: b := print(s)   | $(pc = 1) \land (s' = a[i] + s) \land (i' = i + 1)$                 |

|                     | $\land (pc' = ite(i+1 < 100), 1, 2)) \lor$                          |

|                     | $(pc = 2) \land (b' = call(print, s)) \land pc' = exit$             |

Figure 5.1: A block program and its transition system

on the translation validation procedure Validate which is introduced in [PZP00] and [ZPL01], we define the AValidate procedure, a variation of Validate, which better fits block programs. The procedure describes how to produce the verification conditions, sufficient to prove that the target system  $\mathcal{S}^T$  refines the source system  $\mathcal{S}^S$ . AValidate uses some constructions without describing how to implement them. Based on these constructions, a set of verification conditions is produced. The soundness of AValidate implies that every concrete implementation of these constructions, is a sound proof of the translation validation.

The AVALIDATE procedure is defined as follows:

1. Construct a control abstraction mapping

$$\kappa: \{B_0^T, \dots, B_{exit}^T\} \longmapsto \{B_0^S, \dots, B_{exit}^S\},\$$

such that  $\kappa(0) = 0$  and  $\kappa(exit) = exit$ . Also, the mapping  $\kappa$  should preserve location observability, i.e.  $\beta^T(i)$  iff  $\beta^S(\kappa(i))$ , where i is a block index.

- 2. For each block  $B_i$  of the target system, form an invariant  $\varphi_i$ , that states a target property which should hold true whenever pc = i. Also,  $\varphi_0 = true$ . Only target variables may appear in  $\varphi_i$ .

- 3. Construct a data abstraction mapping

$$\alpha: \bigwedge_{V \in V^S \wedge V \neq pc} (V = E_v(V^T)) \wedge PC = \kappa(pc),$$

where  $E_v$  is a (possibly conditional) expression over target variables. For example:

$$x = case \ p_1 : e_1; \ p_2 : e_2; \ otherwise \ e_3;$$

.

It is required that for every  $i \in \beta^T : \varphi_i \wedge \alpha \to O = o^1$ . The data abstraction  $\alpha$  is a mapping, which maps every target state  $s^t$  to a source state  $s^s$ , such that  $\langle s^s, s^t \rangle \models \alpha$

4. For each  $i \in \{0, ..., n\}$  a block index in  $P^T$ , construct a verification condition  $VC_i$ :

$$\varphi_i \wedge \alpha \wedge \alpha' \wedge \rho_i^T \rightarrow$$

$$(\bigvee_{j \in succ(B_i)} (pc' = j) \land \varphi'_j) \land \qquad (5.1a)$$

$$(\rho_{\kappa(i)}^S \lor \qquad (5.1b)$$

$$(Pres(V^S) \land e < c \land e' > e \land pc' \notin \beta^T)) \qquad (5.1c)$$

$$(\rho_{\kappa(i)}^S \lor \tag{5.1b})$$

$$(Pres(V^S) \land e < c \land e' > e \land pc' \notin \beta^T)) \tag{5.1c}$$

where e is an integer valued expression which depends on the target variables. The disjunct  $Pres(V^S)$  allows a non-singleton sequence of target states to be mapped to a single source state (stuttering). The constraint  $e < c \land e' > e$  is needed, in order to bound the length of such stuttering sequence. In this constraint, e is an integer valued expression and c is an integer constant.  $\alpha'$  is  $\alpha$ , where each source or target variable is replaced by its primed version.

5. Establish the validity of the verification conditions.

It is also allowed to add auxiliary variables to the target system, as needed. Auxiliary variables are program variables, to which assignments are added inside a program, not for influencing the flow of control or the computation, but in order to assist in the verification of the translation (see [AL91], [MP95]-page 144).

Let  $\sigma^S: s_0, s_1, \ldots$  and  $\sigma^T: t_0, t_1, \ldots$  be source and target computations respectively. A contracting mapping from  $|\sigma^T|$  to  $|\sigma^S|$  is a surjective function  $f: |\sigma^T| \longrightarrow |\sigma^S|$ , such that f(0) = 0 and  $f(i+1) \in \{f(i), f(i)+1\}$  for every i,

<sup>&</sup>lt;sup>1</sup>We recall that capital letters are used for source system variables, and small letters are used for target system variables.

$0 < i+1 < |\sigma^T|$ . For an abstraction mapping  $\alpha$ , we say that the computation  $\sigma^S$  is  $\alpha$ -related to  $\sigma^T$  if there exists a contracting mapping  $f: |\sigma^T| \longrightarrow |\sigma^S|$  such that  $\langle s_{f(i)}, t_i \rangle \vDash \alpha$ , for every  $i < |\sigma^T|$ .

#### 5.3 Soundness of the AVALIDATE Procedure

Let  $S^S = \langle V^S, O^S, O_L^S, \Theta^S, \rho^S \rangle$  and  $S^T = \langle V^T, O^T, \beta^T, \Theta^T, \rho^T \rangle$ , be a source transition system and a target transition system respectively. We want to prove that if the verification conditions are valid, then  $S^T$  refines  $S^S$ . The proof includes:

- 1. Proving that if  $\sigma = s_0^T, \ldots, s_i^T, \ldots$  is a computation of the target system  $\mathcal{S}^T$ , then  $\varphi_j$  holds at  $s_i^T$  where  $s_i^T[pc] = j, j = 0, \ldots, n$  and  $i < |\sigma^T|$ .

- 2. Showing that for each target computation  $\sigma^T$  there exists a corresponding computation  $\sigma^S$  of the source system.

- 3. Showing that the observation trajectories induced by  $\sigma^T$  and  $\sigma^S$  are  $\alpha$ -related.

#### Proving the invariants

Let  $\sigma = s_0^T, \ldots, s_i^T, \ldots$  be a computation of  $S^T$ . The proof is done by induction on *i*. The base case is trivially true  $(\varphi_0 = true)$ .

Let  $\varphi_{s_i^T[pc]}$  be valid at state  $s_i^T$  of the computation.

Induction step:  $\varphi_{s_{i+1}^T[pc]}$  holds at  $s_{i+1}^T$  because  $s_{i+1}^T$  follows  $s_i^T$  in the computation, hence  $s_{i+1}^T[pc] \in succ(s_i^T)$  and  $\langle s_i^T, s_{i+1}^T \rangle \vDash \rho^T$ , in particular  $\langle s_i^T, s_{i+1}^T \rangle \vDash \rho^T_{s_i[pc]}$  (see claim 1). The validity of the verification condition  $VC_{s_i^T[pc]}$  proves that  $\varphi_{s_{i+1}^T[pc]}$  holds at state  $s_{i+1}^T$  (see 5.1a).

We showed that if for each  $i \in \{0, \ldots, n\}$ ,

$$\varphi_i \wedge \rho_i^T \to \bigvee_{j \in succ(B_i)} (pc' = j) \wedge \varphi_j'$$

(5.2)

then  $\varphi_j$  holds at  $s_i^T$  where  $s_i^T[pc] = j, \ j = 0, \ldots, n$  and  $i < |\sigma^T|$ . Since the invariants are target system invariants in which source system variables do not appear, and the mapping  $\alpha$  defines the source variables in terms of target variables, we may ignore the conjuncts  $\alpha$  and  $\alpha'$  which appear in the verification conditions.

#### Constructing a corresponding source computation

We first define a computation prefix.

**Definition 2** Computation prefix - Let  $S = \langle V, O, \beta, \Theta, \rho \rangle$  be a transition system, and  $\sigma = s_0, \ldots, s_N$  be a sequence of states of S such that  $s_0 \models \Theta$  and, for all  $i, 0 \le i \le N-1$ , we have  $\langle s_i, s_{i+1} \rangle \models \rho$  then  $\sigma$  is a computation prefix of S.

Let  $\sigma^T = t_0, \ldots, t_i, \ldots, 0 \le i < |\sigma|$ , be a computation of the target system  $S^T$ . We inductively construct a source computation which is  $\alpha$ -related to  $\sigma^T$ .

The construction considers increasing prefixes  $\sigma_j^T: t_0, \ldots t_j$  of the computation  $\sigma^T$  and shows how to construct a corresponding  $\alpha$ -related prefix  $\sigma_j^S$ . Together with the construction of  $\sigma_j^S$ , we also inductively define the construction mapping f.

As the base case, we take  $\sigma_j^T: t_0$  and  $\sigma_j^S: s_0$ , where  $s_0$  is obtained by mapping  $t_0$  to values of the variables  $V^S$  according to  $\alpha$ . We also define f(0) = 0. Obviously  $\sigma_0^S$  is  $\alpha$ -related to  $\sigma_0^T$ .

Next assume that we have already constructed the prefix  $\sigma_j^S: s_0, \ldots s_k$  corresponding to the prefix  $\sigma_j^T: t_0, \ldots t_j$ , and defined the value of f(i), for all  $i=0,\ldots,j$ , We will show how to construct  $\sigma_{j+1}^S$  and define f(j+1). Let  $i=t_j[pc]$ . By induction we know that f(j)=k and that  $s_k$  and  $t_j$  are  $\alpha$ -related. In case i=exit,  $\sigma_j^T$  is the complete target computation, and we are done. Otherwise,  $j<|\sigma^T|$  and there exists a successor state  $t_{j+1}$ . Let  $V_j^T$  and  $V_{j+1}^T$  denote the values of the variables  $V^T$  at states  $t_j$  and  $t_{j+1}$  respectively. Let  $V_j^S$  and  $V_{j+1}^S$  denote their respective  $\alpha$  images. Consider the expression

$$\varphi_i(V_i^T) \wedge \alpha(V_i^S, V_i^T) \wedge \alpha(V_{i+1}^S, V_{i+1}^T) \wedge \rho_i^T(V_i^T, V_{i+1}^T)$$

which is obtained from the sub-formula  $\varphi_i \wedge \alpha \wedge \alpha' \wedge \rho_i^T$  by the substitution

$$\gamma: \left[ V^T \longleftarrow V_j^T, (V^T)' \longleftarrow V_{j+1}^T, V^S \longleftarrow V_j^S, (V^S)' \longleftarrow V_{j+1}^S \right]$$

We claim that this expression evaluates to 1 (true). The invariant  $\varphi_i(V_j^T)$  holds due to part 1 of the proof and the fact that  $pc_j = i$ . The mapping  $\alpha(V_j^S, V_j^T) = \alpha(V_{j+1}^S, V_{j+1}^T) = 1$  because we computed  $V_j^S$  and  $V_{j+1}^S$  using  $\alpha$ . The transition relation  $\rho_i^T(V_j^T, V_{j+1}^T)$  holds because  $t_{j+1}$  is a  $\rho^T$ -successor of  $t_j$ .

Since  $VC_i$  is assumed to be valid, it follows that the r.h.s of this implication holds under the substitution  $\gamma$ . We consider two cases:

Case I: The r.h.s of  $VC_i[\gamma]$  holds due to the disjunct 5.1b  $(\rho_{\kappa(i)}^S)$ . Then, we take  $\sigma_{j+1}^S = \sigma_j^S$ ;  $s_{k+1}$ , where  $s_{k+1} = \alpha(t_{j+1})$  which implies  $s_{k+1}[V^S] = V_{j+1}^S$ . Obviously  $s_{k+1}$  is a successor of  $s_k$  since  $\langle s_k, s_{k+1} \rangle \models \rho_{\kappa(i)}^S$  and, by the induction hypothesis  $\alpha$ -relating  $t_j$  to  $s_k$ ,  $s_k[pc] = \kappa(i)$ . In this case, we define f(j+1) = k+1 = f(j)+1. It is obvious that  $\sigma_{j+1}^S$  and  $\sigma_j^T$ ;  $s_{j+1}$  are  $\alpha$ -related.

Case II: The r.h.s of  $VC_i[\gamma]$  holds due to the disjunct (5.1c). Note that this is possible only if  $i \notin \beta$ , that is, i is not an observation-requiring location. In this case, we take  $\sigma_{j+1}^S = \sigma_j^S$  and define f(j+1) = f(j) = k. Due to the conjunct  $Pres(V^S)$ , we know that  $V_{j+1}^S = V_j^S$ , which shows that  $t_{j+1}$  and  $s_k$  are  $\alpha$ -related (due to  $\alpha(V_{j+1}^S, V_{j+1}^T)$ ). It follows again that  $\sigma_{j+1}^S$  and  $\sigma_{j+1}^T = \sigma_i^T; s_{j+1}$  are  $\alpha$ -related. Case II can be consecutively repeated only a bounded number of times due to the bounded progress measure e.

#### The Observations Induced by $\sigma^S$ and $\sigma^T$ are $\tau$ -related

In the previous part we have shown how to construct a source computation  $\sigma^S$  which is  $\alpha$ -related to a given target computation  $\sigma^T$ . We now consider the induced observation trajectories  $\omega^S$  and  $\omega^T$  and show that they are of equal length and their respective observations are  $\tau$ -related. According to the construction, whenever a state  $t_j$  was associated with an observation-requiring location i, we could not use case II, which implies that f(j+1)=f(j)+1. As a result, while a source state  $s_k$  which is not observation-requiring can be mapped to an arbitrary long (but finite) sequence of target states, each observation-requiring state corresponds to a unique target state. It follows that between  $\sigma^S$  and  $\sigma^T$  there is a 1-1 correspondence between the observation-requiring states. Since these are the only states retained while forming an observation sequence, we conclude that  $|\omega^S| = |\omega^T|$ . Furthermore, let  $t_j$  and  $s_j$  be two states corresponding to the same observation, and let  $t_j[pc] = i \in \beta$ . Since  $\varphi_i$  holds at  $t_j$ , and  $s_j$ ,  $t_j$  are  $\alpha$ -related, the implication  $\varphi_i \wedge \alpha \to O = o$  leads to  $s_j[O] = t_j[o]$ .

# Chapter 6

# Loop Unrolling

#### 6.1 Description of the Optimization

Loop unrolling generates more opportunities for instruction-level parallelism by duplicating the code of the loop's body a number of times equal to the unrolling factor. Instead of moving the control to the beginning of a loop body, at the end of an iteration (in the case that the loop termination condition is not met), the body of the loop is copied by the compiler, one or more times, and the control is moved to the next instruction. Loop unrolling is a preparatory optimizer stage, which enables further optimizations. When the number of loop iterations is known to the compiler, this stage is followed by elimination of branch instructions at the end of most iterations, thus increasing the basic block size. In other cases, the unrolled loop instructions are rescheduled, so as to avoid stalling of the processor pipeline and to obtain a better parallelization [LE95].

Figure 6.1 gives a schematic description of loop unrolling optimizer stage. The left side of the figure describes the source loop, where the number of iterations is N. The right side describes the optimized loop, with unrolled loop factor of C. The target loop iterates  $((N-1) \operatorname{div} C) + 1$ . The last target iteration may not be completed. Another difference between the source and the target loops is the value of the loop counter. In the source program it assumes all values between 0 to N, while in the optimized program its values are  $0, C, 2C, \ldots, N$ .

Figure 6.1: General form of loop unrolling

#### 6.2 Validating Loop Unrolling

In this section we describe the data and control abstraction mapping that can be used in the framework of the AVALIDATE procedure in order to produce the verification conditions required to prove the validity of loop unrolling optimization. To validate this particular optimization technique, there is no need to compute invariants as described in the second step of the procedure AVALIDATE, and we can use the invariant  $\varphi = true$ .

We consider the general loop unrolling form which is presented in figure 6.1. We assume that BODY is only one block, knowing that this optimization is usually applied to the most-inner loop. For simplicity, we also assume that BODY code does not change I or N. Usually, loop unrolling is not applied in cases which violate this assumption. Consequently, a similar assumption is made for the target's body. According to the AVALIDATE procedure, we first have to construct the control abstraction mapping. The target loop is divided into C blocks, all of them are mapped into the loop body block of the source. Thus, the control mapping  $\kappa$  is:  $(\kappa(l0) = L0) \wedge \ldots \wedge (\kappa(l1.1) = l0) \wedge \ldots \wedge (\kappa(l1.1))$

|                       | Target Unrolled Loo                                     | p                                                             |           | contd.                                                               |                                                                        |

|-----------------------|---------------------------------------------------------|---------------------------------------------------------------|-----------|----------------------------------------------------------------------|------------------------------------------------------------------------|

| 10:<br>11_1:<br>11_2: | <pre>i:= 0;  body; aux := 1; branch(i&gt;=n-1) l2</pre> | $ \begin{cases} & \text{First} \\ & \text{copy} \end{cases} $ | l1_(k+1): |                                                                      |                                                                        |

| l1_k:                 | <pre>body;<br/>aux := k;<br/>branch(i&gt;=n-2) 12</pre> | } k'th copy                                                   | 11_C:     | <pre>body; i := i+C; aux := 0; branch(i<n) l1<="" pre=""></n)></pre> | $\left.\begin{array}{c} \text{Last} \\ \text{copy} \end{array}\right.$ |

|                       |                                                         |                                                               | 12:       |                                                                      |                                                                        |

Figure 6.2: Adding an auxiliary variable

$$\ldots = \kappa(l1\_c) = L1) \wedge (\kappa(l2) = L2).$$

An auxiliary variable aux, is added at the end of each copy of the body, as shown in figure 6.2, in order to enable a valid data abstraction outside the loop. The auxiliary variable is needed, because exiting from the target loop can occur at any location inside the target loop. We could equally use  $N \mod C$ , but in order to simplify automatic validation of the verification condition, we choose to add an auxiliary variable. The data abstraction  $\alpha$  is:

$$(pc \leq l1\_1 \rightarrow I = i) \land pc = l1\_2 \rightarrow I = i+1 \dots \land$$

$(pc = l1\_C \rightarrow I = i+C-1) \land (pc = l2 \rightarrow I = i+aux) \land (N = n) \land \dots$

Verification conditions are needed for each  $l1\_k$  (k = 1, ..., C). For example,  $VC_{l1\_1}$ , in Fig. 6.3 is produced for the first copy of body (k = 1), whereas the verification condition for the last copy of body (k = C) is presented in Fig. 6.4.

Appendix A shows a complete example of the validation process of loop unrolling optimization. The compiler we use is the TRIMARAN compiler

$$VC_{l1\_1}: \\ \alpha: \begin{cases} (pc \leq l1\_1 \rightarrow I = i) \land (pc = l1\_2 \rightarrow I = i + 1) \land \dots \land \\ (pc = l1\_C \rightarrow I = i + C - 1) \land \\ (pc = l2 \rightarrow I = i + aux) \land (N = n) \land (PC = \kappa(pc)) \land \dots \end{cases} \\ \alpha': \begin{cases} (pc' \leq l1\_1 \rightarrow I' = i') \land (pc' = l1\_2 \rightarrow I' = i' + 1) \land \dots \land \\ (pc' = l1\_C \rightarrow I' = i' + C - 1) \land \\ (pc' = l2 \rightarrow I' = i' + aux') \land (N' = n') \land (PC' = \kappa(pc')) \\ \land \dots \end{cases} \\ \rho_{l1\_1}^T: \begin{cases} (pc = l1\_1) \land \rho_{body}^T \land (pc' = ite(i \geq n - 1, l2, l1\_2)) \land \\ (aux' = 1) \land (i' = i) \land (n' = n) \end{cases} \\ \rightarrow \\ \rho_{L1}^S: \begin{cases} (PC = L1) \land \rho_{BODY}^S \land (I' = I + 1) \land \\ (PC' = ite(I < N, L1, L2)) \land (N' = N) \end{cases}$$

Figure 6.3: Verification condition for the first copy

$$VC_{l1\_k}: \quad \alpha \wedge \alpha' \wedge$$

$$\rho_{l1\_C}^T: \begin{cases} (pc = l1\_C) \wedge \rho_{body}^T \wedge (pc' = ite(i + C < n, l1\_1, l2)) \wedge \\ (aux' = 0) \wedge (i' = i + C) \end{cases}$$

$$\rightarrow$$

$$\rho_{L1}^S: \begin{cases} (PC = L1) \wedge \rho_{BODY}^S(V^S, V^{S'}) \wedge (I' = I + 1) \wedge \\ (PC' = ite(I + 1 < N, L1, L2)) \wedge (N' = N) \end{cases}$$

Figure 6.4: Verification condition for copy Number C

41

[TR0]. A special proof rule was implemented in STEP [BBC<sup>+</sup>95] by Henny Sipma to support code validation. The user provides source and target transition systems, data abstraction and invariants. Upon invoking the proof rule, STEP automatically produces the verification conditions. Then, the verification conditions are mechanically, though interactively, proved by STEP[BBC<sup>+</sup>95].

# Chapter 7

# Software Pipelining

#### 7.1 Architecture Definition

In this section we define the syntax of a pseudo machine code, VIR - virtual intermediate representation, for a virtual architecture, based on the IA64 family of architectures. This syntax conforms with that of block programs, as defined in 5.1. To simplify the presentation, we prefer not to use the original machine-language syntax, but to present machine programs in a higher-level, C-like, programming style. In particular, we use "do-while" instead of conditional branch, which is used to implement loops. In other cases we use "if-else" instead of conditional branch. However, the actual implementation works directly on the genuine IA64 machine language syntax.

#### 7.1.1 Machine Registers

The processor has the following registers:

- $\mathbf{r}_i \ (1 \leq i \leq m)$  A general integer register.

- 1c- Loop counter register. A special register which counts the iterations within a loop and controls the loop completion.

- $t_i$  ( $1 \le i \le n$ )- An integer register in the rotating register file.

•  $p_i$  (1  $\leq i \leq l$ )- A one bit register, called *predicate register*, in the rotating predicate register file.  $\vec{p}$  is the vector of all the predicate registers.

#### 7.1.2 Machine Instructions

Assigning a value to a memory variable is a *store-to-memory* instruction. The occurrence of a memory variable on the right side of an assignment, stands for a *memory-load* instruction. Thus,  $a := t_1$  stands for storing the value of register  $t_1$  into memory variable a. Direct assignment of a memory variable to another memory variable is not allowed, since this instruction is not supported by the underlying machine. Arithmetic instructions are used with their usual meaning. We use *wait* to indicate no operation. Usually, this is used when the CPU waits for the completion of an instruction, such as a *load-from-memory*.

A special syntax represents the rotation of the register file:

$$\langle t_n := t_{n-1} := \cdots := t_1 \rangle$$

with the following semantics:  $t'_n = t_{n-1} \wedge \cdots \wedge t'_2 = t_1$ . An equivalent notation is used for the rotation of the predicate register file. The predicated execution feature of the architecture, is expressed by using an "if  $(p_{c_k})$ " prefix. Before starting a loop with N iterations and with Sc pipeline stages, the predicate array  $\vec{p}$  is initialized to  $10^{Sc-1}$  (equally written as  $\vec{p} := 10^{Sc-1}$ ). This means that the first predicate register is initiated to 1 and, the remaining Sc-1 predicate registers are initiated to 0. All instructions, appearing on a single command line, are executed in parallel within a single step. In other cases, the parallel execution is deduced from the context<sup>1</sup>.

#### 7.1.3 Architecture Support for Software Pipelining

Software pipelining is a technique that takes advantage of advanced architecture features, such as parallelism (multiple memory and arithmetic

<sup>&</sup>lt;sup>1</sup>Note that although instructions may be executed in parallel, the architecture defines the semantics of parallel execution, to be the same as the sequential execution of the instructions' sequence.

units), rotating register file, predicate register and special branch instructions [AJLA95, Huf93]. Software pipelining increases the loop throughput by overlapping the loop's iterations, that is, by initiating successive iterations before the completion of previous ones, and achieving saturation of functional units. To pipeline a loop, the compiler should find an instruction schedule that best utilizes the functional units, to achieve minimal execution time, yet without causing a register jam.

One technique for loop scheduling is  $Modulo\ Scheduling\ [RST92]$ . To find an overlapped schedule, the compiler must take into account the constraints imposed by the availability of functional units and registers. Suppose that execution of one iteration takes c cycles. Considerations of the data dependencies within the loop body and instructions latency lead to a calculation of an initiation interval - Int. Int is the number of instruction cycles issued for iteration i, before iteration i+1 can be initiated. Let  $O_1, O_2$  be two instructions using the same machine resource, which are scheduled to cycles  $c_1$  and  $c_2$  of a loop body, respectively. Then, it is required that  $(c_1 \mod Int)$  be different from  $(c_2 \mod Int)$ . When all such constraints are satisfied, we have a sound  $modulo\ schedule$ . It looks as though the loop body is divided into stages whose execution time is Int cycles. The number of stages is Sc = c/Int

To demonstrate the modulo scheduling technique consider the C program in Fig. 7.1. In this loop, there is no data dependency between the iterations.

```

int a[100], b[100], N;

main {

int I:=0;

do {

a[I]:=b[I]+5;

I++;

} while(I < N);

}</pre>

```

Figure 7.1: C source program

The target program that appears in Fig. 7.2, is expressed in VIR, without any optimization. Since the *load* delay is 2 cycles, one iteration time is 4

```

\begin{aligned} &\mathbf{i}_1 := 0; \ \mathbf{i}_2 := 0; \ \mathbf{1c} := 0; \\ &\mathbf{do} \\ &\{ \\ &\mathbf{t}_1 := \mathbf{b}[\mathbf{i}_1]; \ \mathbf{i}_1 := \mathbf{i}_1 + 1; \\ & \quad - \mathbf{Load} \\ & \quad wait \ one \ cycle \ for \ the \ load \ delay \ to \ expire; \\ &\mathbf{t}_2 := \mathbf{t}_1 + 5; \\ &\mathbf{-Add} \\ &\mathbf{a}[\mathbf{i}_2] := \mathbf{t}_2; \ \mathbf{i}_2 := \mathbf{i}_2 + 1; \\ &\mathbf{1c} + +; \\ &\} \text{while } (\mathbf{1c} < \mathbb{N}); \end{aligned}

```

Figure 7.2: Unoptimized target code

cycles. For this loop, the compiler calculates an initiation interval of 1 cycle. The number of stages Sc, is thus 4. Pipelining can be achieved by initiating source iteration i+1, one cycle after iteration i. A pipelined execution of the resulting instruction scheduling for this loop is demonstrated in Fig. 7.3 with N, number of iterations, equal to 6. ld stands for load, w for wait, st for store and st add for add. st add stands for execution instruction st of source iteration st. For example, st add stands for the load instruction of iteration number 2.